- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1935EB (Analog Devices, Inc.) 4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

Preliminary Technical Data

AD1935/AD1936/AD1937/AD1938/AD1939

Rev. Pr

I

| Page 23 of 30

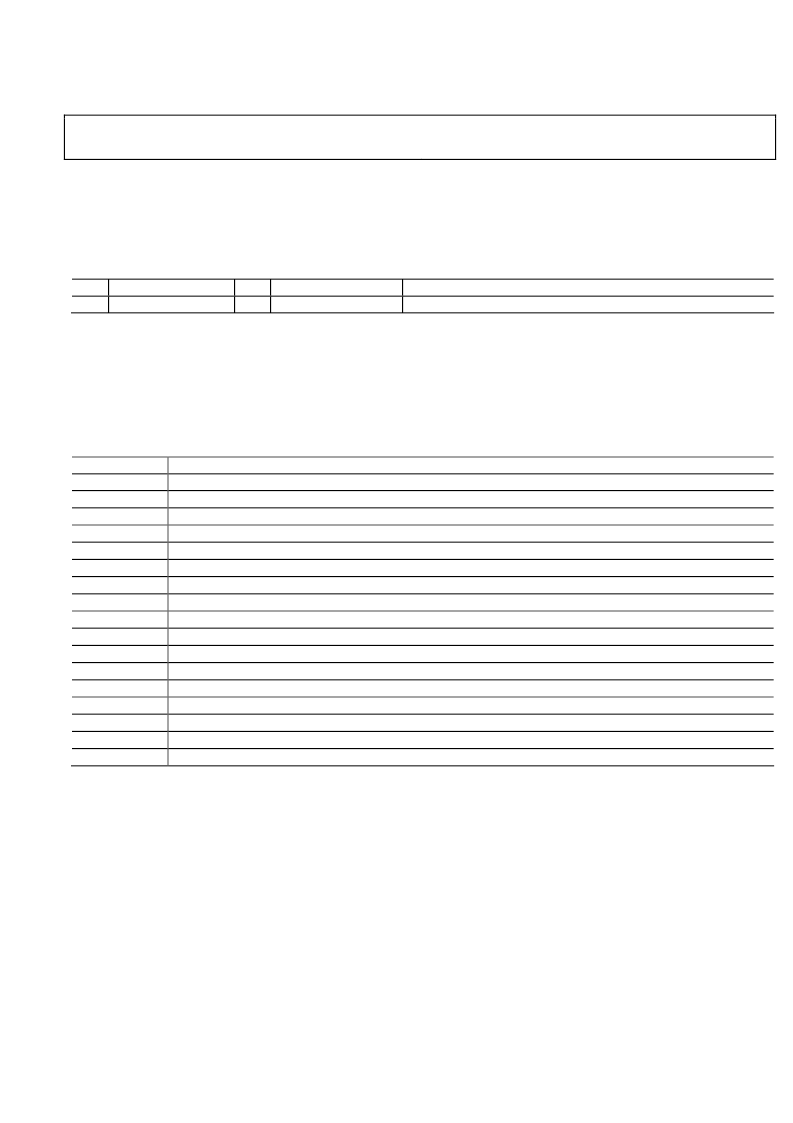

REGISTER DEFINITIONS

Register format

Bit

Global Address

23:17

R/W

16

Register Address

15:8

Data

7:0

Table 16

Note 1: The format is the same for I

2

C and SPI.

Note 2: Global address for the AD193X series is 0x04, shifted left 1 bit due to the R/W bit.

Note 3: In I

2

C, ADR0 and ADR1 are ORed into bits 17 and 18 to provide multiple chip addressing.

Note 4: All registers are reset to 0, except for the DAC volume registers which are set to full volume.

Register addresses and functions

Address

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Function

PLL and Clock Control 0

PLL and Clock Control 1

DAC Control 0

DAC Control 1

DAC Control 2

DAC Individual Channel Mutes

DAC 1L Vol Control

DAC 1R Vol Control

DAC 2L Vol Control

DAC 2R Vol Control

DAC 3L Vol Control

DAC 3R Vol Control

DAC 4L Vol Control

DAC 4R Vol Control

ADC Control 0

ADC Control 1

ADC Control 2

Table 17

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1936EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

Eval-AD1940EB

SigmaDSP-TM Multichannel 28-Bit Audio Processor

EVAL-AD1953EB

16-bit fixed point DSP with Flash

EVAL-AD1958EB

PLL/Multibit DAC

EVAL-AD1959EB

PLL/Multibit DAC

EVAL-AD1974EB

4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAl-AD1974EBZ

4 ADC with PLL, 192 kHz, 24-Bit Codec

相关代理商/技术参数

EVAL-AD1936EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937AZ

功能描述:BOARD EVAL FOR AD1937 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-AD1937EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937EBZ

制造商:Analog Devices 功能描述:EB SINGLE CHIP CODEC 4 ADC'S W/DIFF OUTP - Boxed Product (Development Kits)

EVAL-AD1938AZ

功能描述:BOARD EVAL FOR AD1938 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-AD1938EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24-Bit CODEC

EVAL-AD1938EBZ

制造商:Analog Devices 功能描述:EVAL BD FOR MULTI CHANNEL 96KHZ CODEC - Boxed Product (Development Kits)

EVAL-AD1939AZ

功能描述:BOARD EVAL FOR AD1939 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板